An open standard for high-performance peripheral connectivity.

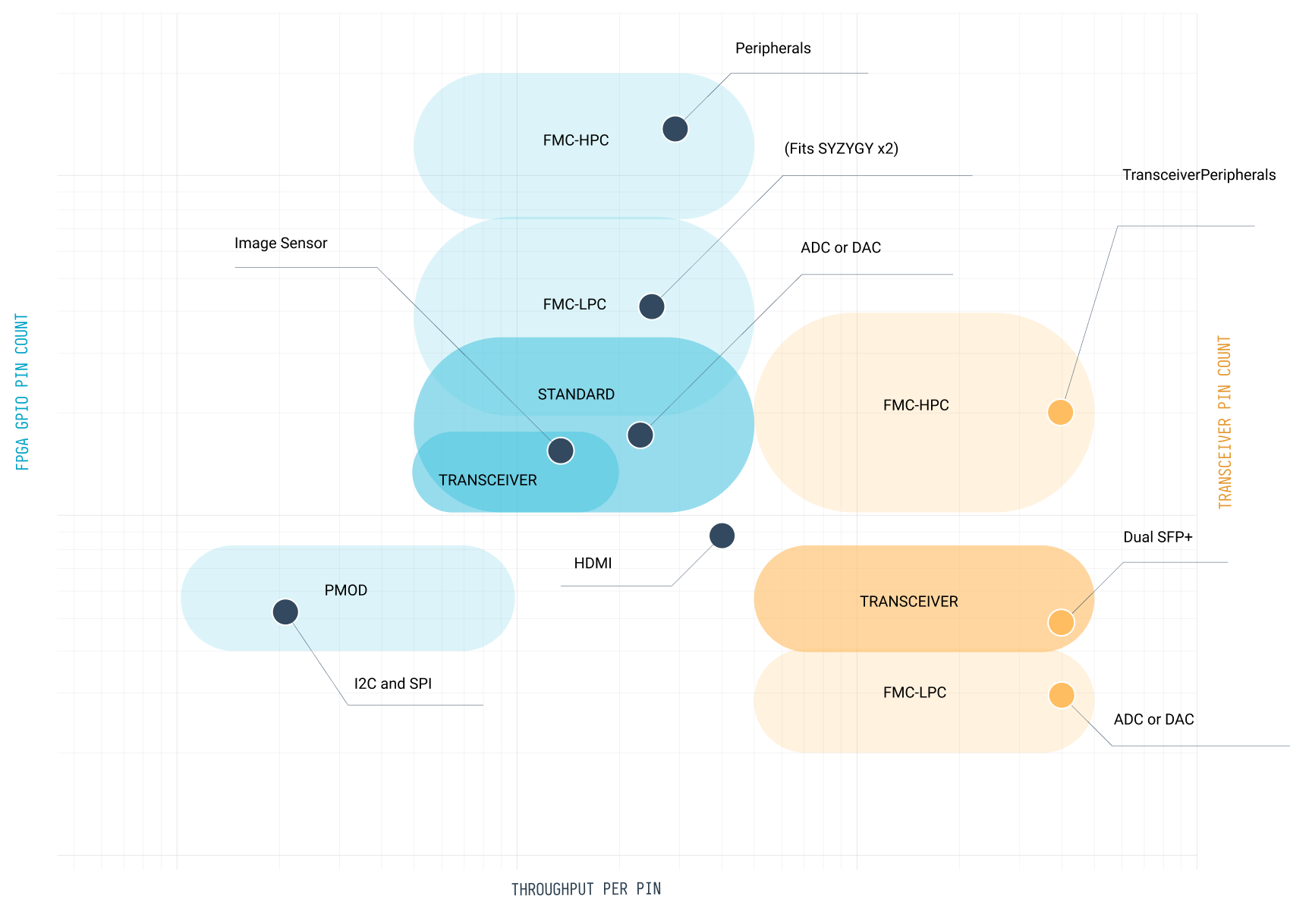

| Interface | Pin Count | MHz / Pin | ||

|---|---|---|---|---|

| Min | Max | Min | Max | |

| PMOD | 4 | 8 | 1 | 50 |

| SYZYGY STD | 10 | 32 | 50 | 500 |

| SYZYGY XCVR | 10 | 18 | 50 | 200 |

| SYZYGY XCVR (gigabit pins) | 4 | 8 | 500 | 5,000 |

| FMC LPC | 20 | 72 | 50 | 500 |

| FMC LPC (gigabit pins) | 2 | 4 | 500 | 5,000 |

| FMC HPC | 72 | 200 | 50 | 500 |

| FMC HPC (gigabit pins) | 10 | 40 | 500 | 5,000 |